基于Legup的FPGA开发

在上一节文章中,我们全面梳理了HLS中开源软件Legup的基本概念,接下来我们将解读Legup的使用说明,以及FPGA算法编译烧录的相关概念。

安装部署

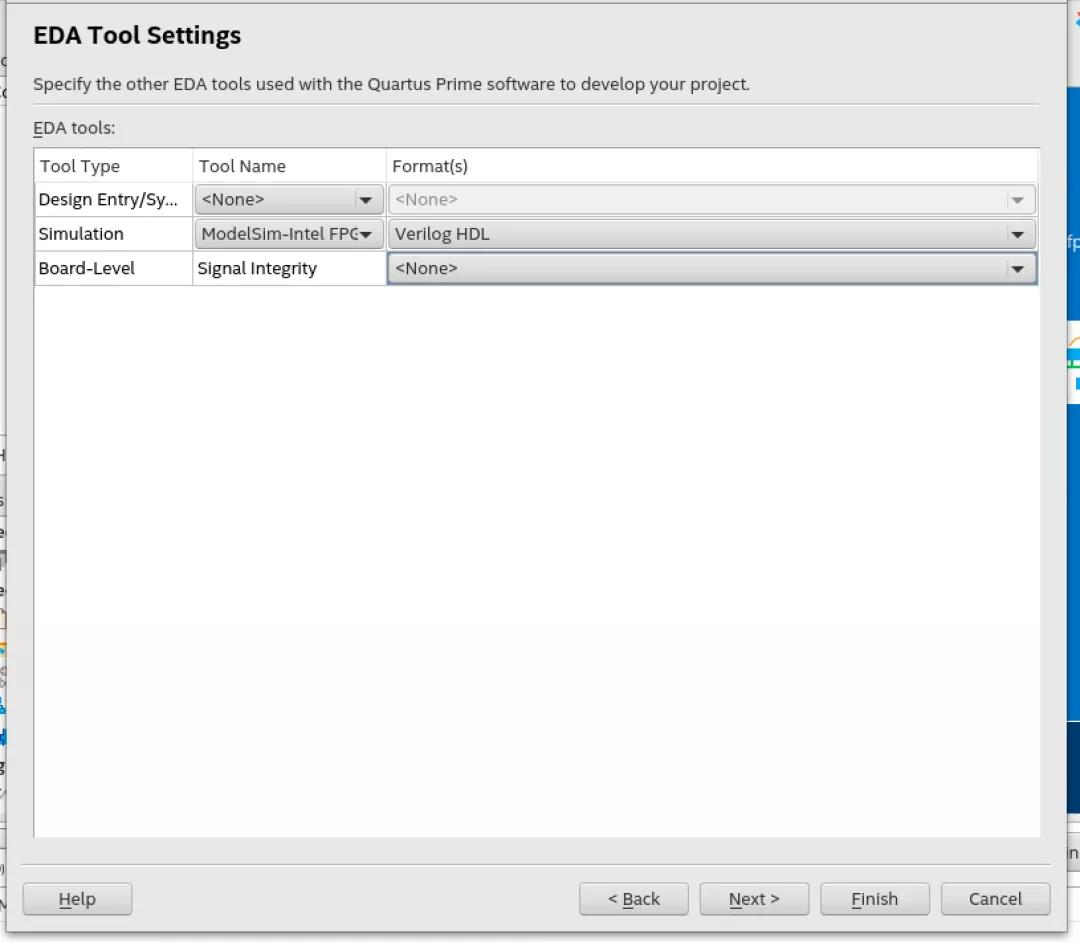

由于Legup在编译和仿真时,会依赖Quartus和Modelsim工具,所以请事先安装好这两个工具,这里不做过多说明,基于已有的Quartus虚拟机进行安装。操作系统是centos7.4

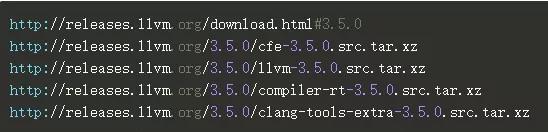

♦ 安装LLVM-3.5

下载需要的软件:

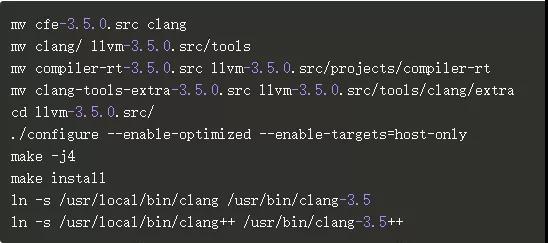

编译安装:

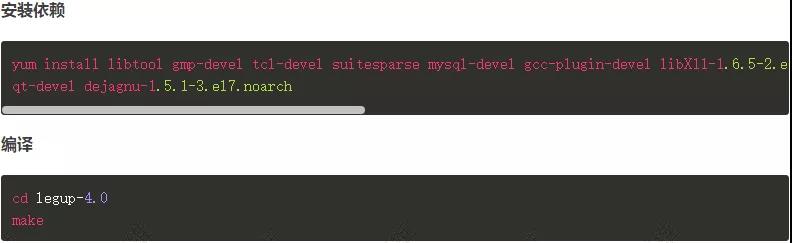

♦ 安装Legup-4.0

下载源码

排查测试

♦ 错误排查

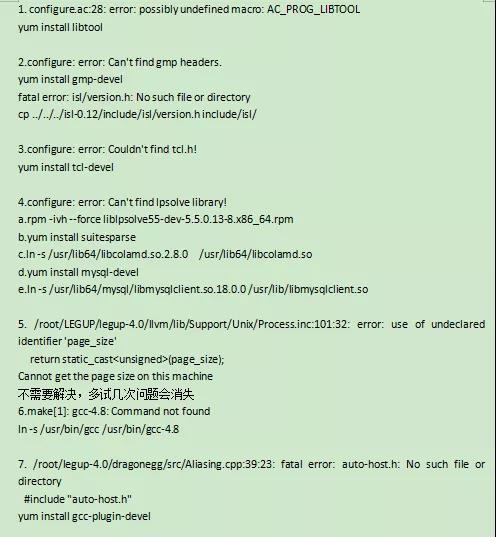

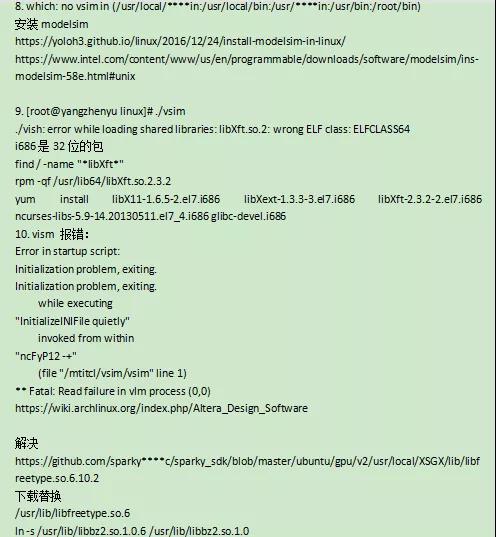

在编译过程中会有各种各样的依赖错误,下面记录了主要的问题,部分问题在前面的安装依赖里已经解决了。

滑动查看更多

♦ 测试

通过测试命令批量测试,可以查看测试通过情况。

cd examples

runtest

跑测试demo sra.c

cd examples/sra

make

此时可以看到生成了 sra.v 文件,这就是最终的Verilog代码。

使用说明

在编译过程中会有各种各样的依赖错误,下面记录了主要的问题,部分问题在前面的安装依赖里已经解决了。

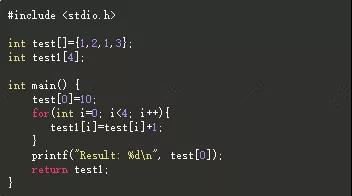

♦ 编写C程序

两个全局变量,test和test1,逻辑也很简单,最终输出test1应该等于{11,3,2,4}

♦ 编译Verilog代码:

# make

# produces verilog: test.v

../../llvm/Release+Asserts/bin/llc -legup-config=../legup.tcl -march=v test.bc -o test.v

仿真输出:

make v

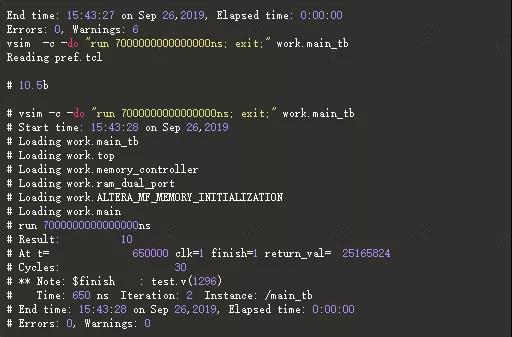

输出如下:

可以看到输出结果:return_val= 25165824,C程序里的输出是一个数组,但是这里的输出却是一个十进制值。根据前面的说明可以知道这里的输出是没有意义的。要查看具体输出,可以通过modelsim仿真。

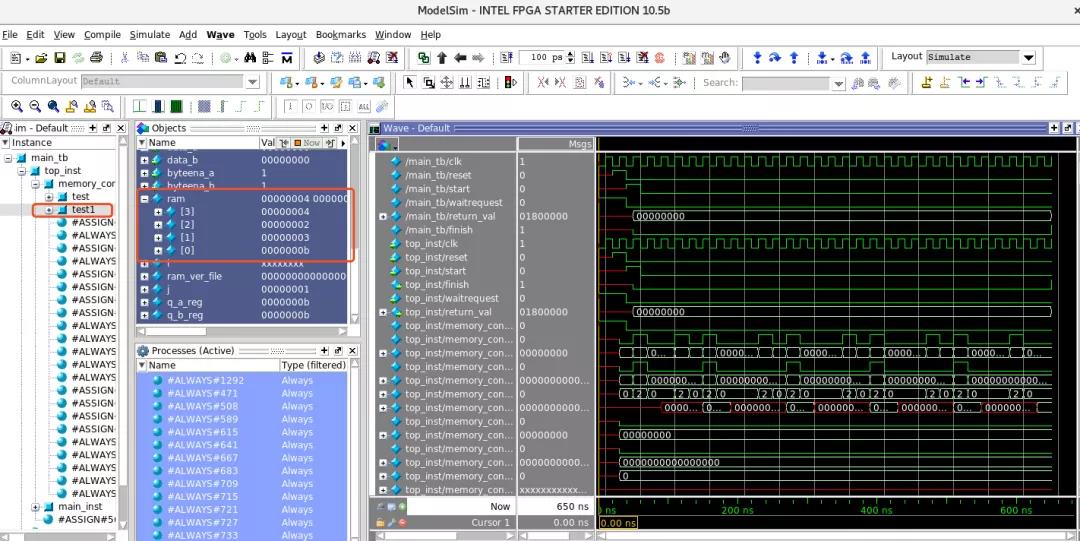

需要系统有图像界面,仿真:

make w

可以看到上图的仿真结果,test1的ram值是{11,3,2,4}与前面的值相同,说明HLS结果没有问题。

烧录到FPGA

♦ 生成sof文件

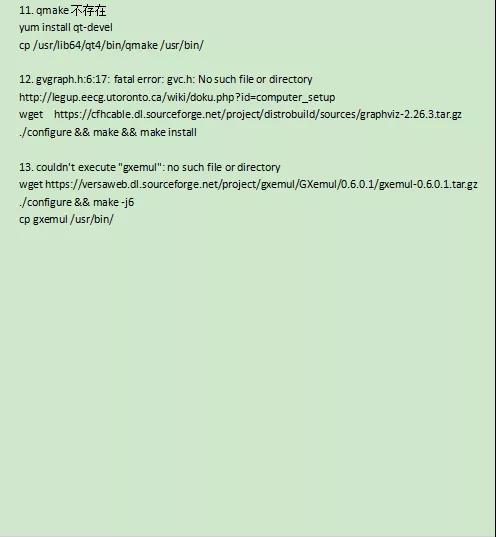

向FPGA里烧录,需要生成sof文件,创建quartus项目:

滑动查看更多

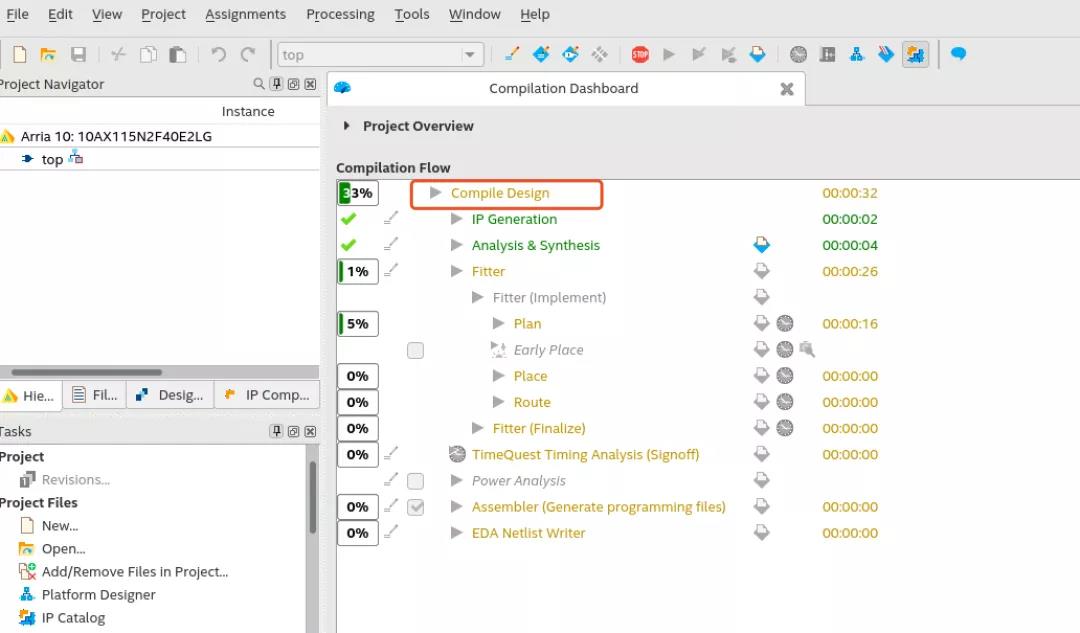

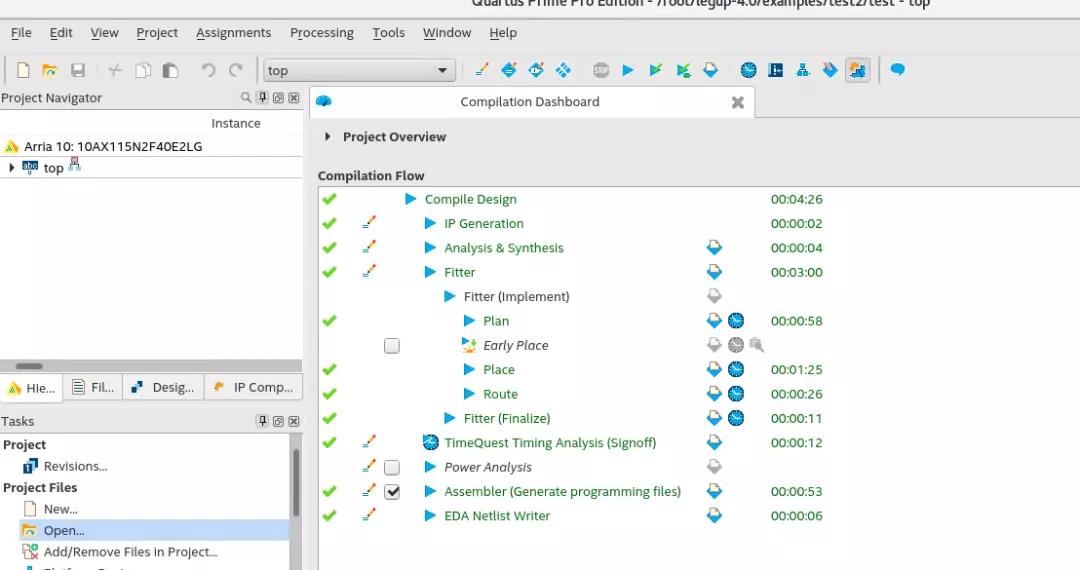

创建好项目之后,进行全编译:

滑动查看更多

编译完成,查看是否生成sof文件

du -sh output_files/top.sof

36M output_files/top.sof

等待生成sof文件,之后可以通过Jtag烧录如FPGA开发板中。

本文主要介绍了FPGA开发工具HLS的开源软件Legup的基本概念和使用,以及FPGA算法编译烧录的相关概念。后面会继续介绍Legup的开源插件LeFlow,可以将TensorFlow实现的python代码转换为Verilog代码。

杨振宇,海云捷迅资深系统架构师,成都信息工程大学计算机应用技术硕士研究生毕业,10余年软件开发和架构经验,熟悉Linux,OpenStack,Kubernetes,Docker等开源技术并具有开源社区贡献经历,在云计算、人工智能、物联网等技术领域有较深的研究和丰富的一线开发经验。

学习更多FPGA专业知识,关注“FPGA在线培训”:(点击了解更多培训资讯)。FPGA在线培训囊括了业内的前沿技术理论,汇集了业内经验丰富的一线工程师,将带领学员全方位解读开发语言、开发工具、配置电路等FPGA开发设计环节。