工业 4.0 和物联网的长远前景毋庸置疑,但前提是必须达到关键的技术要求,只有这样才能充分发挥其潜力。这些要求包括无处不在的连接性、7 天 24 小时全天候的可用性、低延迟,以及最重要的,从“传感器到云端”全面的端到端安全性。最重要的安全要求包括:保护物联网设备及其生成、处理和传输的数据、符合相关标准的要求,确保供应链的安全性,同时达到性能要求、无缝可用性和易用性。

企业们面临的一个主要挑战是,将上述高级别安全要求转化为贯穿在产品中具体、安全的实施过程。但是,由于之前遗留的各种硬件架构、缺乏针对工业安全要求的标准、安全性与(功能)安全之间相互重叠和混淆,以及某些情况下缺乏关于安全性的知识和术语,企业在具体实施过程中面临着艰巨的挑战。

目前绝大多数安全实施都以在软件中实施加密协议为基础,最常见的是使用第三方加密软件库,这类软件库通过通用处理器编译和执行,并使用市场中常见的操作系统。

基于软件的现代安全实施总体十分复杂,因此为恶意第三方提供了多个潜在目标(从技术角度来说,“攻击面”很大),包括但不限于:

· 操作系统;

· 设备驱动程序;

· 加密原语的实施(例如使用第三方密码库);

· 编译器优化和各代处理器之间可能的微架构更改;

· 软件堆栈的深度;

· 高速缓存和内存管理;

· 密钥管理 — 例如,缓冲区溢出可能泄露一切,包括密钥;

· 缺乏对安全算法实施的完全控制。

除了上述列表外,基于软件的安全实施还可能无法满足性能需求(吞吐率和/或延迟)。在许多情况下,功耗也是一个挑战。

重要的是,软件库(包括加密库)和操作系统(在工业系统的整个生命周期内的)一般会经常更新,用户在系统维护上也面临着重重困难。例如,在物联网设备的整个生命周期(可能跨越几十年),设备必须通过更新来获得漏洞修复。这是一项艰巨的任务,而且会大大增加基于软件的安全解决方案的总体拥有成本。

随着行业在安全思维领域的不断发展,人们对底层处理器架构的安全性提出了质疑。虽然人们下意识地假设之前的底层硬件处理器非常安全,但最近披露的可能利用处理器微架构的性能增强优化(例如,无序执行和预测分支执行)(Meltdown、Spectre、Foreshadow)使这一基本假设受到质疑。之前提到的大多数安全漏洞都已经修补过了,但依然无法消除信息披露的可能性。

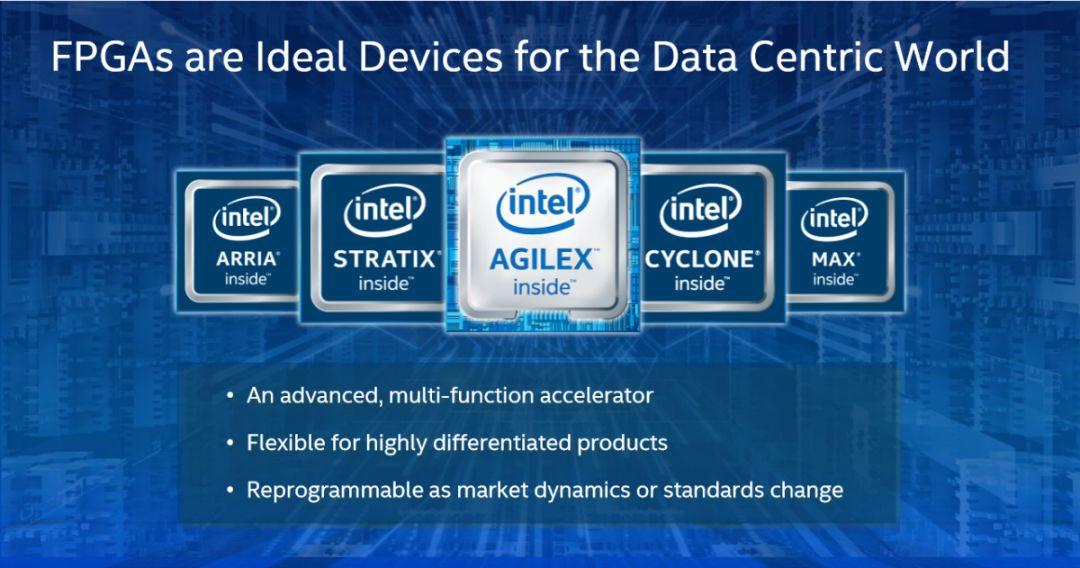

市场上的绝大多数 FPGA 都基于易失性 SRAM 技术,这意味着 FPGA 的功能由外部非易失性内存中的配置文件指定。现代 FPGA 产品家族支持已加密和已验证配置,其中配置文件永远不会以明文的形式存储在外部非易失性配置内存中,而且在 FPGA 启动期间,FPGA 会对配置文件内容进行解密和身份验证。

在安全实施方面,可重编辑逻辑(FPGA)的传统用例是通过提升加密协议中关键算法的性能,卸载主机处理器。常用于实现加速的设计技巧包括流水、并行化和循环展开。对称加密,例如 AES,尤其能够实现这种加速 — 以及成本节省与功耗降低。

然而,基于 FPGA 的安全实施所具备的优势并不仅仅在于性能提升,因为在 FPGA 逻辑中适当实施安全功能也会提高最终产品的安全级别。

基于 FPGA 的加密实施还具备以下技术优势:

· 算法和协议的灵活性和可更新性;

· 可以利用内置 FPGA 安全特性;

– 经过加密和验证的配置;

– 防篡改特性;

– 部分重配置(在指定情况下);

– 可在硬件中实现红黑分离的设计方法;

· 更严格的算法实施控制,包括重要的密钥管理。

在实践中,基于 FPGA 实施安全协议会利用多个知识产权(IP)模块的组合。

到目前为止,绝大多数安全漏洞的出现,都是由于攻击者精心利用了基于软件的安全与加密实施中所存在的弱点。FPGA 是基于硬件的安全设计的理想选择,因为其具备出色的可重新编程性,支持设计阶段加密算法和安全协议的各种迭代,同时支持设计人员完全控制和了解整个实施过程。基于 FPGA 的安全性通常使用 IP 模块组合来构建完整的安全协议,包括密钥管理。

内容源自英特尔FPGA