SRIO 在某无线通信系统中的应用(二)

本文将继续介绍SRIO在无线通信中的运用及各项数据测试结果,浅析SRIO的发展空间。

SRIO接口实现

SRIO接口实现的系统框图如图3所示。在发端,业务通过 SGMII 接口进入DSP,对数据进行比特级信号处理,包括扰码、解扰、CRC校验、Turbo编码译码以及速率匹配等。处理后的数据经由SRIO进入FPGA内部,进行符号级信号处理,包括组帧、查分编码、成型滤波等,然后由DA发送出去。

在收端,经由AD 接收的数据,经过符号级信号处理,包括AGC、信道滤波、同步检测、匹配滤波、解调以及均衡后,经SRIO发送到 DSP,在 DSP 内再经过速率匹配、Turbo 译码、CRC 校验以及解扰发回PC机,完成整个业务流程。

图3 SRIO接口实现的系统框图

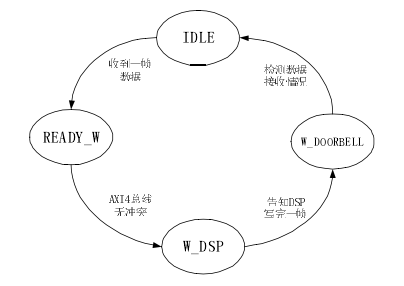

在此设计中,FPGA与DSP的SRIO通信时,FPGA处于主动。发送方向为:上电时,DSP往FPGA发送一个Doorbell,告诉FPGA写数据包的地址,在FPGA收到一帧数据后,如果AXI4总线检测无冲突,则FPGA通过SRIO往DSP发送数据包,当一帧数据发送完毕,再发送一个 Doorbell给DSP告诉一帧数据发送完毕。整体流程如图 4 所示。

图4 FPGA 中 SRIO 发送状态机示意图

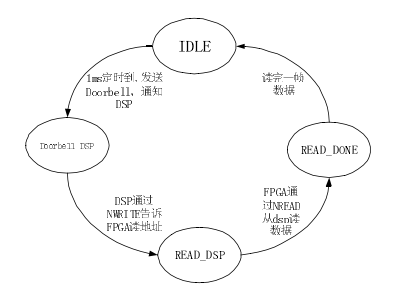

图5 FPGA 中 SRIO 接收状态机示意图

在接收方向,每1ms,FPGA会往 DSP发送一个Doorbell,告诉 DSP此时FPGA需要数据,DSP通过NWRITE写给FPGA一个包,告诉FPGA取数据包的地址,然后FPGA通过NREAD去读一帧数据,发送给信号处理模块,其流程如图 5 所示。

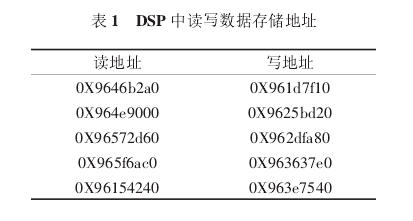

其中读地址在5个地址中随机变化,因此需要在读取数据时,由DSP临时通知。读写地址情况如表 1 所示。

系统测试

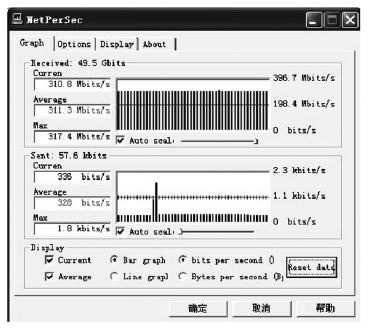

在测试中,使两套设备互连,射频用馈线连接,分别做300M、150M、64M、32M的带宽切换,传输带宽、质量以及灵敏度满足要求,详细测试数据如表2所示。在实测中,最大带宽可达 310M,符合设计要求,如图 6 所示。

图6 最大带宽传输测试数据

SRIO发展空间

经过设计,本系统最大带宽需求为 300Mb/s,而测试中实际最大带宽已达 310Mb/s,因此将 SRIO应用于此通信系统,完全满足系统吞吐量的要求。设计中使用的 2.5GX4 的设计,实际最大数据传输速率不到 4G,SRIO 传输还有较大空闲,可适应以后更大带宽、更大通信速率的需求。

总结

在上一篇文章(SRIO 在某无线通信系统中的应用一)中,我们认识到通讯系统对高速接口的需求性及SRIO的高性能,本文则通过系统测验,进一步探索了SRIO的可实施性及发展空间,为通讯系统发展提出新的实现方案。

作者简介

万毅,英特尔® FPGA中国创新中心FPGA架构师,电子科技大学通信与信息系统硕士研究生毕业,10年以上开发和架构经验,熟悉Altera、ACtel、Xilinx以及国产深圳国微FPGA的开发流程以及开发工具,在以太网MAC、网络数据转发、高速接口、时序分析与约束、FPGA+ARM以及FPGA soc软硬协同方面有丰富的开发经验。