不久前曾为筒子们展示过在PAM4模式下,英特尔® Agilex™收发器中的E-Tile即使在电缆长度超过规范要求的情况下也能够达到58Gb/s速率的测试视频(戳英特尔® Agilex™ FPGA收发器技术揭秘之E-Tile性能测试大起底)。而现在,仅过了短短几个月,这一数字就翻了一倍哦。

英特尔发布的一段新视频展示了以 116 Gbps 速度运行(采用 PAM4 调制)的高速长距 (LR) 收发器测试芯片的最新性能结果。该收发器测试芯片采用英特尔 10 纳米制程技术构建,满足 CEI-112G-LR-PAM4 规范的最高数据速率要求。测试芯片支持 116 Gbps 运行速度,表明高速收发器设计针对现有 100/200/400 千兆以太网 (GbE) 标准留有更多空间,且支持新兴协议和前向纠错 (FEC)标准。

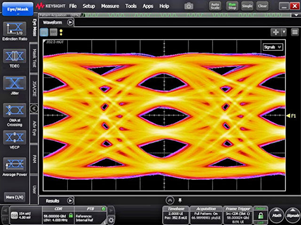

视频还展示了收发器芯片的传输器通过互连和外部电缆向同一个芯片上的接收器发送 116 Gbps PRBS31 数据模式,芯片上 BGA 球之间总插入损耗超过 35 dB。在测试中,收发器芯片的性能比 CEI-112G-LR-PAM4 规范的原始误码率 (BER) 要求高出近三个数量级,甚至达到了 116 Gbps。此处的截屏显示了示波器测量的收发器芯片的发射器以 116 Gbps 运行时的去嵌入式 PAM4 眼图。

I/O 收发器芯片的传输器以 116 Gbps 运行时去嵌入式后测量的 PAM4 眼图

用于该芯片的基于高速长距数字 ADC 和 DAC 的收发器架构以及硬化的 100/200/400 GbE 协议堆栈将被整合到英特尔® Agilex™ I 系列 FPGA 中,它面向云、企业和边缘应用的高速带宽密集型网络进行了优化。

此处是 116 Gbps PAM4 收发器 I/O 芯片视频: