2019年 7 月 20 日,是阿波罗 11 号登月 50 周年纪念日,这是人类第一次踏上地球以外的天体。为庆祝这一纪念日,人们计划开展或已经开展了许多纪念活动。但从工程角度而言,或许最有意义的一项活动当属来自旧金山湾区的一支团队,他们修复了一台 Block II 阿波罗导航计算机 (AGC)。

修复团队包括 Marc Verdiell(加利福尼亚州阿瑟顿)、Ken Shirriff(加利福尼亚州雷德伍德城)、Carl Claunch(加利福尼亚州洛思阿图斯)和 Mike Stewart(南旧金山)。该团队进行了长达数月的 AGC 恢复工作。这台存在争议的 AGC 归 Jimmie Loocke 个人所有,他在阿波罗太空计划期间担任美国宇航局的热真空测试技术员。他在 20 世纪 70 年代购买了 2 吨重的 NASA 剩余设备,其中就包括这台 AGC。(这本身是一个不同寻常的故事。)

这台 AGC 帮助执行了阿波罗 11 号、12 号、13 号、14 号、15 号、16 号和 17 号飞往月球并返航以及将所有宇航员送上月球的任务。阿波罗命令模块 (CM) 中的 AGC 从地球导航到月球并再次返回。月球模块 (LM) 中的另一个 AGC 帮助降落在月球上,然后从月球起飞,并与月球轨道上的 CM 会合。

AGC与摩尔定律的历史“交点”

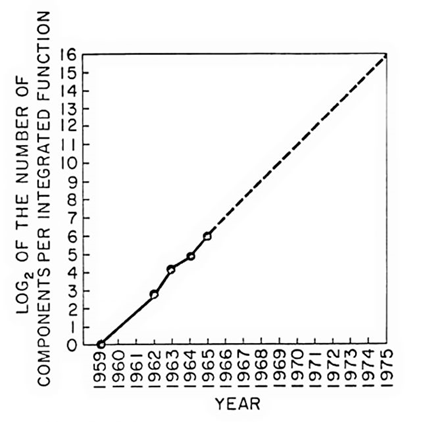

AGC 是一台具有重要历史意义的计算机,其中原因有很多。其中一个原因就是 AGC 与摩尔定律的关系。几乎所有电子行业的人,特别是半导体行业的人,都熟悉摩尔定律以及戈登摩尔于 1965 年绘制的图表,他就是根据这个图表制定了摩尔定律的概念。摩尔使用五种特定的半导体设备绘制该图表,直到现在,没人能够回想起这五个点所代表的设备。然而,山景城计算机历史博物馆的半导体馆长 David Laws 将两个早期的半导体工件放在一起,对摩尔定律图进行逆向工程设计。

戈登摩尔制定摩尔定律所用的图表中包含 5 个现有的半导体器件。第二个点代表用于设计原始 Block I 阿波罗导航计算机的 IC。

摩尔定律故事与 AGC 故事的相交点位于原摩尔定律曲线的一个特定点上。这是第二个点,代表 Fairchild Semiconductor μLogic Type G RTL IC。这个器件的历史太长,现在几乎没人知道“μLogic”和“Type G”这两个术语的含义。“RTL”最初是指“电阻晶体管逻辑”,而现在的含义完全不同。在 FPGA 领域和数字芯片设计领域,“RTL”代表“寄存器传输级”。其实,根本不是一回事。

Fairchild Semiconductor μLogic Type G RTL IC 是一个 3 输入 NOR 门。没错,每个集成电路有一个门。每个芯片一个门代表了 1962 年前后半导体制造领域的最佳状态。

那时候,IC 的未来并不确定。例如,1960 年 EDN 杂志上的一篇文章指出:

导弹和太空电子设备的主要问题是电池和太阳能电池的重量和尺寸,而不是电子组件的尺寸…

“标准模块是否实用仍然是业内的争议焦点。”

然而,美国宇航局对 AGC 的尺寸和重量施加了严格的限制,以符合阿波罗计划的总体设计预算。因此,当美国宇航局选择由麻省理工学院的仪器实验室开发阿波罗计划的 AGC 时,计算机设计人员知道他们需要使用当时最具革命性、最轻便的小型电子设备技术来开发 AGC。符合这一条件的技术就是 Type G IC。

1962 年 2 月 27 日,麻省理工学院仪器实验室以单价 43.50 美元(1962 年的价值)的价格订购了 100 个 Fairchild μLogic Type G IC,以用于评估。在几个月内,麻省理工学院仪器实验室得出结论,IC 非常适合用于阿波罗导航计算机,并使用其中的 4100 实施 Block I AGC 设计中的所有逻辑。到 1965 年,AGC 计划已经购买了大约 200,000 个 G 型逻辑芯片,均价为每个 20 美元到 30 美元。IC 的未来变得非常光明。

快进到今天。半个世纪以来,Jimmie Loocke 的 Block II AGC 一直没有开过机,运行状况不明。

该团队在恢复 Loocke 的 AGC 的过程中遇到了很多障碍,最终没能赶上阿波罗 11 号登月 50 周年纪念日庆典。特定障碍(本博文的基础)已嵌入 AGC 的内存中。

Cyclone® IV FPGA助力AGC内存修复挑战

AGC 是使用两种类型的内存设计的:RAM 和 ROM。然而,半导体内存尚未发明,因此 AGC 的 ROM 是磁绳内存,RAM 是磁芯内存。

您可能熟悉核心内存。从 1953 年到 1971 年,它一直在计算机内存领域占据主导地位。在 20 世纪 50 年代和 60 年代设计的大型机和小型机都使用核心内存作为 RAM。核心内存在数千个手工编织成线栅的铁氧体环中存储“1”和“0”。手工制作的核心内存价格昂贵,因为它是手工制作的,不是特别紧凑。虽然为实现核心内存制造自动化做了许多努力,但这些努力基本上都是徒劳无功的。而后在 1970 年 10 月,英特尔推出了第一款大型半导体内存:1 KB 1103 DRAM。在短短几年内,DRAM 完全取代了核心内存,因为它更密集、更快、更便宜。核心内存长达 20 年的主导地位就这样突然消失了,1103 DRAM 成为英特尔第一个重要的革命性产品。

尽管与核心内存相关,但磁绳内存不太常见,主要用于航空航天应用。计算机程序实际上是手工编织成磁绳内存的,因此每个磁绳内存组件都是独一无二的。若要更改程序,您需要以物理方式更换磁绳内存模块。手工编织程序是一项昂贵的劳动密集型工作,因此半导体 ROM 在上市后很快就取代了磁绳内存。

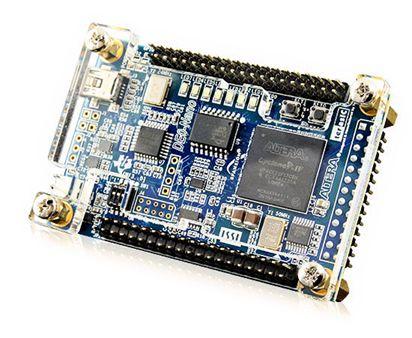

Jimmie Loocke 购买了没有任何磁绳内存模块的 AGC,这台计算机的核心内存最终却无法使用(尽管后来被修复)。然而,这些内存相关挑战并没有阻止 AGC 的修复工作。AGC 修复团队成员之一 Mike Stewart 之前使用原始 AGC 原理图复制了 AGC 硬件。尽管存在一些设计挑战,他还是成功地在 FPGA 中复制了整个 AGC,包括其核心和磁绳内存的功能。具体而言,他在DE0-NanoFPGA 开发板内部(基于 Cyclone® IV FPGA)创建了 AGC 硬件仿真,使用英特尔® Quartus® Prime 软件套件复制 AGC 的设计。

Terasic DE0-Nano 开发板

在 Stewart 为复制 AGC 所需要克服的众多设计挑战中,将该计算机基于 3 输入 NOR 门的异步 RTL 逻辑设计转换为同步 FPGA 逻辑是最严峻的一个挑战。他通过将 FPGA 的逻辑元件转换为时钟 NOR 门来解决这一挑战。时钟会减慢 FPGA 的逻辑,从而更准确地复制 1962 年基于 RTL NOR 门的实施时序。

因此,当需要用其他东西替换古老 AGC 缺失的磁绳内存和非运行核心内存时,Stewart 有一个现成的解决方案:他已经准备好在 Cyclone® IV FPGA 中使用 AGC 磁绳和核心内存仿真了。Steward 只需将 Terasic DE0-Nano 开发板的 3.3V 逻辑连接到 AGC 的 4V 逻辑(带一些电平转换器)即可。

他就是这样做的。

内容源自英特尔FPGA